| Document Identifier: DSP0238 | 2 |

|------------------------------|---|

| Date: 2021-03-02             | 3 |

| Version: 1.2.0               | 4 |

|                              |   |

**5 Management Component Transport Protocol**

- 6 (MCTP) PCIe VDM Transport Binding

- 7 Specification

- 8 Supersedes: 1.1.0

- 9 Document Class: Normative

- 10 Document Status: Published

- 11 Document Language: en-US

**Copyright Notice** 13 14 Copyright © 2009, 2018, 2021 Distributed Management Task Force, Inc. (DMTF). All rights reserved. 15 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 18 time, the particular version and release date should always be noted. 19 Implementation of certain elements of this standard or proposed standard may be subject to third party patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 21 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 22 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 23 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to 24 any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, 25 disclose, or identify any such third party patent rights, or for such party's reliance on the standard or 26 incorporation thereof in its product, protocols or testing procedures. DMTF shall have no liability to any 27 party implementing such standard, whether such implementation is foreseeable or not, nor to any patent 28 owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is 29 withdrawn or modified after publication, and shall be indemnified and held harmless by any party 30 implementing the standard from any and all claims of infringement by a patent owner for such 31 implementations.

32 For information about patents held by third-parties which have notified the DMTF that, in their opinion,

- 33 such patent may relate to or impact implementations of DMTF standards, visit

- 34 <u>http://www.dmtf.org/about/policies/disclosures.php</u>.

PCI-SIG, PCIe, and the PCI HOT PLUG design mark are registered trademarks or service marks of PCI-SIG.

- 37 All other marks and brands are the property of their respective owners.

- 38 This document's normative language is English. Translation into other languages is permitted.

- 39

# CONTENTS

| 41 |      | reword                                                |   |

|----|------|-------------------------------------------------------|---|

| 42 | Intr | roduction                                             | 5 |

| 43 | 1    | Scope                                                 | 7 |

| 44 | 2    | Normative references                                  | 7 |

| 45 | 3    | Terms and definitions                                 |   |

| 46 | 4    | Symbols and abbreviated terms                         |   |

| 47 | 5    | Conventions                                           |   |

| 48 |      | 5.1 Reserved and unassigned values                    |   |

| 49 |      | 5.2 Byte ordering                                     | 9 |

| 50 | 6    | MCTP over PCI Express VDM transport                   | 9 |

| 51 |      | 6.1 Packet format                                     |   |

| 52 |      | 6.2 Supported media                                   |   |

| 53 |      | 6.3 Physical address format for MCTP control messages |   |

| 54 |      | 6.4 Message routing                                   |   |

| 55 |      | 6.5 Bus owner address                                 |   |

| 56 |      | 6.6 Bus address assignment for PCIe                   |   |

| 57 |      | 6.7 Host dependencies                                 |   |

| 58 |      | 6.8 Discovery Notify message use for PCIe             |   |

| 59 |      | 6.9 MCTP over PCIe endpoint discovery                 |   |

| 60 |      | 6.10 MCTP messages timing requirements                |   |

| 61 | ANI  | INEX A (informative) Notations and conventions        |   |

| 62 | AN   | INEX B (informative) Change log                       |   |

| 63 |      |                                                       |   |

# 64 Figures

| 65 | Figure 1 – MCTP over PCI Express Vendor Defined Message (VDM) packet format | 10 |

|----|-----------------------------------------------------------------------------|----|

| 66 | Figure 2 – Flow of operations for full MCTP Discovery over PCIe             | 17 |

| 67 | Figure 3 – Flow of operations for Partial Endpoint Discovery                | 18 |

| 68 |                                                                             |    |

# 69 Tables

| 70 | Table 1 – PCI Express medium-specific MCTP packet fields              | . 10 |

|----|-----------------------------------------------------------------------|------|

| 71 | Table 2 – Supported media                                             | . 12 |

| 72 | Table 3 – Physical address format                                     | . 12 |

| 73 | Table 4 – Timing specifications for MCTP Control messages on PCIe VDM | . 19 |

| 74 |                                                                       |      |

# Foreword

- 76 The Management Component Transport Protocol (MCTP) PCIe VDM Transport Binding Specification 77 (DSP0238) was prepared by the PMCI Working Group.

- DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems

management and interoperability.

#### 80 Acknowledgments

81 The DMTF acknowledges the following individuals for their contributions to this document:

#### 82 Editors:

- Hemal Shah Broadcom Inc.

- Tom Slaight Intel Corporation

#### 85 Contributors:

- Patrick Caporale Lenovo

- Yuval Itkin NVIDIA Corporation

- Eliel Louzoun Intel Corporation

- Patrick Schoeller Hewlett Packard Enterprise

- 90 Bob Stevens Dell Technologies

# Introduction

The Management Component Transport Protocol (MCTP) over PCIe VDM transport binding defines a

transport binding for facilitating communication between platform management subsystem components

(e.g., management controllers, management devices) over PCIe.

95 The <u>MCTP Base Specification</u> describes the protocol and commands used for communication within and

96 initialization of an MCTP network. The MCTP over PCIe VDM transport binding definition in this

- 97 specification includes a packet format, physical address format, message routing, and discovery

- 98 mechanisms for MCTP over PCIe VDM communications.

# Management Component Transport Protocol (MCTP) PCIe VDM Transport Binding Specification

### 103 **1 Scope**

This document provides the specifications for the Management Component Transport Protocol (MCTP)

transport binding using PCIe Vendor Defined Messages (VDMs).

## 106 **2 Normative references**

107 The following referenced documents are indispensable for the application of this document. For dated 108 references, only the edition cited applies. For undated references, the latest edition of the referenced 109 document (including any amendments) applies.

- 110 CXL Consortium, Compute Express Link<sup>™</sup> (CXL<sup>™</sup>) Specification Revision 1.0,

- 111 <u>https://www.computeexpresslink.org</u>

- 112 CXL Consortium, Compute Express Link™ (CXL™) Specification Revision 1.1,

113 https://www.computeexpresslink.org

- 114 CXL Consortium, Compute Express Link™ (CXL™) Specification Revision 2.0,

115 <u>https://www.computeexpresslink.org</u>

- DMTF DSP0236, Management Component Transport Protocol (MCTP) Base Specification 1.0

<u>https://www.dmtf.org/sites/default/files/standards/documents/DSP0236\_1.0.pdf</u>

- DMTF DSP0236, Management Component Transport Protocol (MCTP) Base Specification 1.3

<u>https://www.dmtf.org/sites/default/files/standards/documents/DSP0236\_1.3.pdf</u>

- 120 DMTF DSP0239, *Management Component Transport Protocol (MCTP) IDs and Codes 1.0* 121 <u>https://www.dmtf.org/sites/default/files/standards/documents/DSP0239\_1.0.pdf</u>

- DMTF DSP0239, Management Component Transport Protocol (MCTP) IDs and Codes 1.8

<u>https://www.dmtf.org/sites/default/files/standards/documents/DSP0239\_1.8.pdf</u>

- ISO/IEC Directives, Part 2, *Rules for the structure and drafting of International Standards,* <u>http://isotc.iso.org/livelink/livelink?func=ll&objld=4230456&objAction=browse&sort=subtype</u>

- 126 PCI-SIG, *PCI Express® Base Specification Revision 1.1*, March 8, 2005,

- 127 <u>http://www.pcisig.com/specifications/</u>

- PCI-SIG, PCI Express® Base Specification Revision 2.0, December 20, 2006,

<u>http://www.pcisig.com/specifications/</u>

- 130 PCI-SIG, PCI Express® Base Specification Revision 2.1, March 4, 2009,

- 131 <u>http://www.pcisig.com/specifications/</u>

- 132 PCI-SIG, PCI Express® Base Specification Revision 3.0, November 10, 2010,

- 133 <u>http://www.pcisig.com/specifications/</u>

- 134 PCI-SIG, PCI Express® Base Specification Revision 3.1a, December 7, 2015,

- 135 http://www.pcisig.com/specifications/

- 136 PCI-SIG, PCI Express® Base Specification Revision 4.0, October 5, 2017,

- 137 <u>http://www.pcisig.com/specifications/</u>

- 138 PCI-SIG, PCI Express® Base Specification Revision 5.0, May 28, 2019,

- 139 http://www.pcisig.com/specifications/

# 140 **3 Terms and definitions**

141 In this document, some terms have a specific meaning beyond the normal English meaning. Those terms142 are defined in this clause.

The terms "shall" ("required"), "shall not", "should" ("recommended"), "should not" ("not recommended"),

"may", "need not" ("not required"), "can" and "cannot" in this document are to be interpreted as described

in <u>ISO/IEC Directives, Part 2</u>, Clause 7. The terms in parentheses are alternatives for the preceding term,

for use in exceptional cases when the preceding term cannot be used for linguistic reasons. Note that

<u>ISO/IEC Directives, Part 2</u>, Clause 7 specifies additional alternatives. Occurrences of such additional

alternatives shall be interpreted in their normal English meaning.

- The terms "clause", "subclause", "paragraph", and "annex" in this document are to be interpreted as

described in <u>ISO/IEC Directives, Part 2</u>, Clause 6.

- 151 The terms "normative" and "informative" in this document are to be interpreted as described in <u>ISO/IEC</u>

- 152 Directives, Part 2, Clause 3. In this document, clauses, subclauses, or annexes labeled "(informative)" do

- 153 not contain normative content. Notes and examples are always informative elements.

- Refer to <u>DSP0236</u> for terms and definitions that are used across the MCTP specifications. For the purposes of this document, the following additional terms and definitions apply.

- 156 **3.1**

#### 157 MCTP PCIe Endpoint

158 a PCIe endpoint on which MCTP PCIe VDM communication is supported

# 159 4 Symbols and abbreviated terms

- 160 Refer to <u>DSP0236</u> for symbols and abbreviated terms that are used across the MCTP specifications. The 161 following symbols and abbreviations are used in this document.

- 162 **4.1**

- 163 **PCle**®

- 164 PCI Express™

- 165 **4.2**

- 166 VDM

- 167 Vendor Defined Message

- 168 **4.3**

- 169 **CXL**™

- 170 Compute Express Link™

# 171 **5 Conventions**

172 The conventions described in the following clauses apply to this specification.

#### 173 5.1 Reserved and unassigned values

- Unless otherwise specified, any reserved, unspecified, or unassigned values in enumerations or othernumeric ranges are reserved for future definition by the DMTF.

- Unless otherwise specified, numeric or bit fields that are designated as reserved shall be written as 0(zero) and ignored when read.

#### 178 5.2 Byte ordering

Unless otherwise specified, byte ordering of multi-byte numeric fields or bit fields is "Big Endian" (that is,the lower byte offset holds the most significant byte, and higher offsets hold lesser significant bytes).

# **181 6 MCTP over PCI Express VDM transport**

- This document defines the medium-specific transport binding for transferring MCTP packets between

endpoints on PCI Express<sup>™</sup> using PCIe Vendor Defined Messages (VDMs).

- A MCTP over PCIe VDM compliant PCIe device shall support MCTP over PCIe VDM communications on at least one PCIe Physical Function (PF) of the device. If a MCTP over PCIe VDM compliant PCI device supports MCTP over PCIe VDM communications on more than one PCIe function, then MCTP over PCIe VDM communication on each function shall be independent from MCTP over PCIe VDM communications on other PCIe functions.

#### 189 6.1 Packet format

- 190 The MCTP over PCI Express (PCIe) VDM transport binding transfers MCTP messages using PCIe Type

- 191 1 VDMs with data. MCTP messages use the MCTP VDM code value (0000b) that uniquely differentiates

- 192 MCTP messages from other DMTF VDMs.

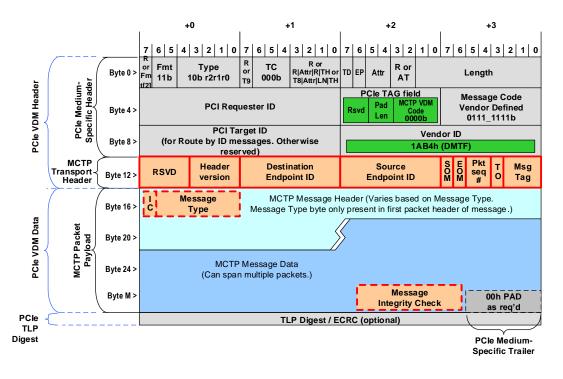

- 193 Figure 1 shows the encapsulation of MCTP packet fields within a PCIe VDM.

# 195

#### Figure 1 – MCTP over PCI Express Vendor Defined Message (VDM) packet format

The fields labeled "PCIe Medium-Specific Header" and "PCIe Medium-Specific Trailer" are specific to carrying MCTP packets using PCIe VDMs. The fields labeled "MCTP Transport Header" and "MCTP Packet Payload" are common fields for all MCTP packets and messages and are specified in <u>MCTP</u>. This document defines the location of those fields when they are carried in a PCIe VDM. The PCIe specification allows the last four bytes of the PCIE VDM header to be vendor defined. The MCTP over PCIe VDM transport binding specification uses these bytes for MCTP Transport header fields under the DMTF Vendor ID. This document also specifies the *medium-specific* use of the MCTP "Hdr Version" field.

Table 1 lists the PCIe medium-specific fields and field values that shall be used in MCTP over PCIe VDM communications. When not specified, field values shall be set according to PCIe specifications. Note that the presence of TLP prefixes in MCTP over PCIe VDM packets is implementation dependent and outside the scope of this specification.

207

#### Table 1 – PCI Express medium-specific MCTP packet fields

| Field  | Description                                                                              |  |

|--------|------------------------------------------------------------------------------------------|--|

| R or   | PCle 1.1/2.0: PCle reserved bit (1 bit).                                                 |  |

| Fmt[2] | PCIe 2.1, 3.X, 4.X, 5.X: Fmt[2]. Set to 0b.                                              |  |

| Fmt    | Format (2 bits). Set to 11b to indicate 4 dword header with data.                        |  |

| Туре   | ype and Routing (5 bits).                                                                |  |

|        | [4:3] Set to 10b to indicate a message                                                   |  |

|        | [2:0] PCI message routing (r2r1r0)                                                       |  |

|        | 000b : Route to Root Complex<br>010b : Route by ID<br>011b : Broadcast from Root Complex |  |

|        | Other routing fields values are not supported for MCTP.                                  |  |

| Field                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R or T9                                     | PCIe 1.1/2.0/2.1/3.X: PCIe reserved bit (1 bit). Refer to the PCI Express <sup>™</sup> specification (PCIe). Set to 0b.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                             | PCIe 4.X/5.X: T9 (1bit). Refer to the PCI Express <sup>™</sup> specification ( <u>PCIe</u> ) Gen 4. Set to 0b.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ТС                                          | Traffic Class (3 bits). Set to 000b for MCTP over PCIe VDM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| R or                                        | PCIe 1.1/2.0: PCIe reserved bits (4 bits). Set to 0000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| R   Attr   R   TH or<br>T8   Attr   LN   TH | PCIe 2.1/3.X: PCIe reserved bit (1 bit), Attr[2] (1 bit) – Set to 0b, reserved bit (1bit), and TH (1bit) – Set to 0b.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                             | PCIe 4.X/5.X: T8 bit (1 bit) – Set to 0b, Attr[2] (1 bit) – Set to 0b, LN (1bit) – Set to 0b, and TH (1bit) – Set to 0b                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TD                                          | TLP Digest (1 bit). 1b indicates the presence of the TLP Digest field at the end of the PCIe TLP (transaction layer packet). The TD bit should be set in accordance with the devices overall support for the TLP Digest capability, and whether that capability is enabled. See description of the TLP Digest / ECRC field, below, for additional information. Note that earlier versions of this specification erroneously required this bit to be set to 0b, which would have required devices to not support the TLP Digest capability. |  |

| EP                                          | Error Poisoned (1 bit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Attr[1:0]                                   | Attributes (2 bits). Set to 00b or 01b for all MCTP over PCIe VDM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| R or                                        | PCIe 1.1: PCIe reserved bits (2 bits).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| AT                                          | PCIe 2.0/2.1/3.X/4.X/5.X: Address Type (AT) field. Set to 00b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Length                                      | Length: Length of the PCIe VDM Data in dwords. Implementations shall support the baseline transmission unit defined in the <u>MCTP Base Specification</u> . For example, supporting a baseline transmission unit of 64 bytes requires supporting PCIe VDM data up to 16 dwords. An implementation may optionally support larger transfer unit sizes.                                                                                                                                                                                       |  |

| PCI Requester ID                            | Bus/device/function or bus/function number of the managed endpoint sending the message.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Pad Len                                     | Pad Length (2-bits). 1-based count (0 to 3) of the number of $0 \times 00$ pad bytes that have<br>been added to the end of the packet to make the packet dword aligned with respect to.<br>PCIe. Because only packets with the EOM bit set to 1b are allowed to be less than the<br>transfer unit size, packets that have the EOM bit set to 0b will already be dword<br>aligned and will thus not require any pad bytes and will have a pad length of 00b.                                                                                |  |

| MCTP VDM Code                               | Value that uniquely differentiates MCTP messages from other DMTF VDMs. Set to 0000b for this transport mapping as defined in this specification.                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Message Code                                | (8 bits). Set to 0111_1111b to indicate a Type 1 VDM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| PCI Target ID                               | (16 bits). For Route By ID messages, this is the bus/device/function number or bus/function number that is the physical address of the target endpoint. This field is ignored for Broadcast and for Route to Root Complex messages.                                                                                                                                                                                                                                                                                                        |  |

| Vendor ID                                   | (16 bits). Set to <b>6836</b> (0x1AB4) for DMTF VDMs. The most significant byte is in byte 10, the least significant byte is byte 11.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RSVD                                        | MCTP reserved (4 bits). Set these bits to 0 when generating a message. Ignore them on incoming messages.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Hdr Version                                 | MCTP version (4 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                             | 0001b : For MCTP devices that conform to the <u>MCTP Base Specification</u> and this version of the PCIe VDM transport binding.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                             | All other settings: Reserved to support future packet header field expansion or header version.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Field                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 00h <b>PAD</b>       | Pad bytes. 0 to 3 bytes of $00h$ as required to fill out the overall PCIe VDM data to be<br>an integral number of dwords. Because only packets with the EOM bit set to $1b$ are<br>allowed to be less than the transfer unit size, packets that have the EOM bit set to $0b$<br>will already be dword aligned, and will thus not require any pad bytes and will have a<br>pad length of $00b$ .                                                                                                                                                                                   |  |  |

| TLP Digest /<br>ECRC | (32 bits). TLP Digest / ECRC (End-to-end CRC). This field is defined for all PCIe TLPs (Transaction Layer Packets). Device support for this field is optional. However, per PCIe v2.1/3.X/4.X/5.X: "If a device Function is enabled to generate ECRC, it must calculate and apply ECRC for all TLPs originated by the Function. If the device supports generating this field, it must support it for all TLPs." Additionally, per PCIe v2.1/3.X/4.X/5.X, if the ultimate PCI Express Receiver of the TLP does not support ECRC checking, the receiver must ignore the TLP Digest. |  |  |

#### 208 6.2 Supported media

This physical transport binding has been designed to work with the following media as defined in <u>DSP0239</u> and listed in Table 2. Use of this binding with other types of physical media is not covered by this specification. Refer to DSP0239 for all supported physical media by MCTP transport bindings.

An implementation that is compliant with this specification shall at least support one of the PCIe media listed in Table 2. Note that the CXL is built on the PCI Express (PCIe) physical and electrical interface.

| Table | 2 – | Supported | media |

|-------|-----|-----------|-------|

|-------|-----|-----------|-------|

| Physical Media Identifier | Description                                 |

|---------------------------|---------------------------------------------|

| 0x08                      | PCIe 1.1 compatible                         |

| 0x09                      | PCIe 2.0 compatible                         |

| OxOA                      | PCIe 2.1 compatible                         |

| 0x0B                      | PCIe 3.X compatible                         |

| 0x0C                      | PCIe 4.X compatible                         |

| 0x0D                      | PCIe 5.X compatible, CXL 1.X/2.X compatible |

## **6.3 Physical address format for MCTP control messages**

216 The address format shown in Table 3 is used for MCTP control commands that require a physical

address parameter to be returned for a bus that uses this transport binding with one of the supported

218 media types listed in 6.2. This includes commands such as the Resolve Endpoint ID, Routing Information

219 Update, and Get Routing Table Entries commands.

| Table 3 – | Physical | address | format |

|-----------|----------|---------|--------|

|-----------|----------|---------|--------|

| Format Size | Address Type                       | Layout and Description |                         |

|-------------|------------------------------------|------------------------|-------------------------|

| 2 bytes     | Bus Device Function (BDF)          | byte 1                 | [7:0] – Bus number      |

| (BDF ID)    |                                    | byto 2                 | [7:3] – Device number   |

| (BDP ID)    |                                    | byte 2                 | [2:0] – Function number |

| 2 bytes     | Alternate Routing Identifier (ARI) | byte 1                 | [7:0] – Bus number      |

| (ARI ID)    |                                    | byte 2                 | [7:0] – Function number |

<sup>220</sup>

#### 221 6.4 Message routing

Physical packet routing within a PCIe bus uses routing as defined by the PCIe specification. PCIe

physical routing/bridging is not the same as MCTP bridging. PCIe physical routing/bridging is generally

transparent to MCTP. There are no MCTP-defined functions for configuring or controlling the setup of a

PCIe bus. The following types of PCIe addressing are used with MCTP messages:

#### • Route by ID

- All MCTP over PCIe VDM packets between endpoints that are not the bus owner shall use Route by ID for message routing.

- 229 The MCTP bus owner shall use Route by ID for messages to individual MCTP endpoints.

230MCTP endpoints are required to capture the PCIe requester ID and the MCTP source EID when231receiving an EID assignment MCTP control request message. This is because this request can232only be issued by the MCTP bus owner.

#### • Route to root complex

- 234 MCTP endpoints shall use this routing for the Discovery Notify request message to the MCTP 235 bus owner as part of the MCTP over PCIe VDM discovery process.

- 236The MCTP endpoints shall use this routing for responding to the MCTP control request237messages that were sent using Broadcast from Root Complex.

- 238 Communication of MCTP PCIe VDM packets that are destined to MCTP bus owner using 239 routed to root complex is implementation specific and is outside the scope of this specification.

#### • Broadcast from root complex

- 241The MCTP bus owner should use this routing for the Prepare for Endpoint Discovery and242Endpoint Discovery messages as part of the MCTP over PCIe VDM discovery process.

- 243

#### 244 **6.4.1** Routing peer transactions on a PCIe bus

Because the PCIe specification does not require peer-to-peer routing support in PCIe root complexes,

MCTP over PCIe VDM messages are not required to be routed to peer devices directly. When peer-to peer routing is not supported by a PCIe root complex, all MCTP over PCIe VDM messages between two

MCTP endpoints shall be routed to or through the MCTP bus owner as an MCTP bridge. If the PCIe root

complex, as the MCTP bus owner, supports peer-to-peer routing, it shall use direct physical addressing to

support routing between two MCTP endpoints on the PCIe bus.

#### 251 6.4.2 Routing messages between PCIe and other buses

- All MCTP messages that span between PCIe and other buses shall be sent through the MCTP bus owner. The MCTP bus owner has the destination EID routing tables necessary to route messages between the two bus segments.

- 255 If an endpoint is aware of multiple routes to a destination over multiple bus types, a higher level

- algorithm/protocol above MCTP shall be used to determine which bus/route to use. Typically this decision

can be based on things like power state and MCTP discovery state.

#### 258 **6.5 Bus owner address**

The MCTP PCIe VDM bus owner functionality shall be accessible through "Route-to-Root Complex" addressing.

#### 261 **6.6 Bus address assignment for PCIe**

262 PCIe bus addresses are assigned per the mechanisms specified in <u>PCIe</u>.

#### 263 6.7 Host dependencies

MCTP over PCIe VDM, when used in a typical "PC" computer system, has a dependency on the host CPU, host software, power management states, link states, and reset. Some of these dependencies are described as follows:

- 267 **Reset**

- Assertion of "Fundamental Reset" on the bus causes both the host functionality as well as the MCTP PCIe VDM communication on an MCTP PCIe endpoint to be reset. From the assertion "Fundamental Reset" until the PCIe fabric has been configured and enumerated, no "MCTP over PCI Express" messages can be sent.

- Similarly, if MCTP PCIe VDM communication is supported on a function, a function level reset

(FLR) could reset MCTP PCIe VDM endpoint as well as MCTP PCIe VDM communication on

that function.

- Configuration and enumeration

- 276Following the de-assertion "Fundamental Reset", the software running on the host CPU277configures and enumerates the PCIe fabric. Failure of the host CPU or boot software to properly278configure and enumerate the PCIe fabric prevents it from being used for MCTP over PCIe VDM279messaging.

#### • Power management states

281 The host (as defined in the context of the PCI Express<sup>™</sup> specification) controls PCIe bus power management. The host may power down PCIe devices and links, or place them in sleep states, 282 283 independent of management controllers, which may cause MCTP PCIe VDM communication to be unavailable. Depending on the device usage in the system, a PCIe device may retain or lose 284 states such as EID, "discovered" state, and routing information (if the device is a bridge). A 285 286 PCIe device that loses MCTP PCIe VDM communication state needs to be reinitialized and/or rediscovered after it returns to a power state that supports MCTP over PCIe VDM 287 288 communication.

• Link states

290The PCIe link states affect MCTP over PCIe VDM communications. MCTP over PCIe VDM291communication can be performed only when the PCIe link is in a state that allows VDM292communications. The mechanisms for PCIe link state transitions are outside the scope of this293specification.

#### • PCle Root Complex

295PCIe Root Complex (RC) is responsible for communicating route-to-root complex MCTP over296PCIe VDM discovery messages to the MCTP bus owner.

## 297 **6.8 Discovery Notify message use for PCIe**

An MCTP control Discovery Notify message shall be sent from a PCIe endpoint to the MCTP bus owner whenever the physical address for the device changes (that is, the endpoint receives a Type 0 configuration write request and the bus number is different than the currently stored bus number). This occurs on the first Type 0 configuration write following a PCIe bus reset during initial enumeration, or during re-enumeration where the bus number has changed (for example, because of a hot plug event, bus reset, and so on).

#### **DSP0238**

304 Endpoints use the Discovery Notify command to inform the MCTP bus owner that it needs to update the

305 endpoint's ID. The Discovery Notify command shall be sent with the PCIe message routing set to 000b

(Route-to-Root Complex), the Destination Endpoint ID for the Discovery Notify message shall be set to 306 the Null Destination EID. The Source Endpoint ID field shall be set to the Null Source EID if the device

- 307 308

- has not yet been assigned an EID; otherwise, it shall contain the assigned EID value.

#### 309 6.9 MCTP over PCIe endpoint discovery

310 This clause describes the steps used to support discovering MCTP endpoints on PCIe.

#### 311 6.9.1 Discovered flag

- 312 Each endpoint (except the bus owner) on the PCIe bus maintains an internal flag called the *Discovered* 313 flag.

- 314 The flag is set to the *discovered* state when the Set Endpoint ID command is received.

- 315 The Prepare for Endpoint Discovery message causes each recipient endpoint on the PCIe bus to set their

- respective Discovered flag to the undiscovered state. For the Prepare for Endpoint Discovery request 316

- message, the routing in the physical transport header should be set to 011b (Broadcast from Root 317 318 Complex).

- 319 An endpoint also sets the flag to the *undiscovered* state at the following times:

- 320 Whenever the PCI bus/device/function or bus/function number associated with the endpoint is • initially assigned or is changed to a different value. 321

- 322 Whenever an endpoint first appears on the bus and requires an EID assignment. A device shall 323 have been enumerated on PCI and have a bus/device/function or bus/function number before it can do this. 324

- 325 During operation if an endpoint enters a state that causes it to lose its EID assignment. •

- 326 For endpoints that have already received an EID assignment but are in any temporary state • where the endpoint was unable to respond to MCTP control requests for more than TRECLAIM 327 328 seconds.

- 329 Only endpoints that have their Discovered flag set to undiscovered shall respond to the Endpoint 330 Discovery message. Endpoints that have the flag set to discovered shall not respond to the Endpoint

- 331 Discovery message.

332 For PCIe endpoints, an Endpoint Discovery broadcast request message can be sent by the MCTP bus owner to discover all MCTP-capable devices. MCTP-capable endpoints respond with an Endpoint 333 334 Discovery response message.

#### 335 6.9.2 PCIe endpoint announcement

336 One or more endpoints may announce their presence and their need for an EID assignment by 337 autonomously sending a Discovery Notify message to the bus owner. This would typically trigger the 338 MCTP bus owner to perform the PCIe endpoint discovery/enumeration processes described in the 339 following subclauses.

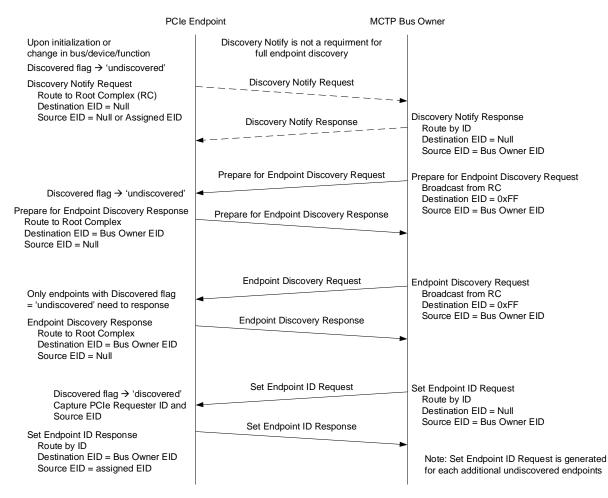

#### 6.9.3 Full endpoint Discovery/Enumeration 340

The following process is typically used when the MCTP bus owner wishes to discover and enumerate all 341 342 MCTP endpoints on the PCIe bus.

343 The MCTP bus owner issues a broadcast Prepare for Endpoint Discovery message. This 1) 344 message causes each discoverable endpoint on the bus to set its PCIe endpoint Discovered

345 flag to undiscovered. Depending on the number of endpoints and the buffer space available in 346 the MCTP bus owner, the MCTP bus owner may not receive all of the response messages. The 347 discovery process does not require the MCTP bus owner to receive all the response messages 348 to the Prepare for Endpoint Discovery request. Because the MCTP bus owner cannot determine that all endpoints have received the Prepare for Endpoint Discovery request, it is recommended 349 that Prepare for Endpoint Discovery request is retried MN1 times to help ensure that all 350 351 endpoints have received the request. The MCTP bus owner is not required to wait for MT2 time 352 interval between the retries.

- The MCTP bus owner should wait for MT2 time interval to help ensure that all endpoints that

received the Prepare for Endpoint Discovery request have processed the request.

- 355

3) The MCTP bus owner issues a broadcast Endpoint Discovery request message. All MCTP 356 capable devices that have their Discovered flag set to undiscovered will respond with an

357 Endpoint Discovery response message.

- Depending on the number of endpoints and the buffer space available in the MCTP bus owner. 358 4) the MCTP bus owner receives some or all of these response messages. For each response 359 message received from an undiscovered MCTP-capable device PCIe bus/device/function or 360 361 bus/function number, the MCTP bus owner issues a Set Endpoint ID command to the physical 362 address for the endpoint. This causes the endpoint to set its Discovered flag to discovered. 363 From this point, the endpoint shall not respond to the Endpoint Discovery command until 364 another Prepare for Endpoint Discovery command is received or some other condition causes 365 the Discovered flag to be set back to undiscovered.

- 3665)If the MCTP bus owner received any responses to the Endpoint Discovery request issued in367Step 3, then it shall repeat steps 3 and 4 until it no longer gets any responses to the Endpoint368Discovery request. In this case, then the MCTP bus owner is allowed to send the next Endpoint369Discovery request without waiting for MT2 time interval. If no responses were received by the370MCTP bus owner to the Endpoint Discovery request within the MT2 time interval, then the371discovery process is completed.

After the initial endpoint enumeration, it is recommended that the MCTP bus owner maintains a list of the unique IDs for the endpoints it has discovered, and reassigns the same IDs to those endpoints if a bus/device/function or bus/function number changes during system operation.

375 Figure 2 provides an example flow of operations for full endpoint discovery.

#### Full PCIe MCTP Endpoint Discovery

- 376

- 377

Figure 2 – Flow of operations for full MCTP Discovery over PCle

#### 378 **6.9.4 Partial endpoint Discovery/Enumeration**

This process is used when the MCTP bus owner wishes to discover endpoints that may have been added

to the bus after a full enumeration has been done. This situation can occur if a device has its

bus/device/function or bus/function number change after the full enumeration has been done, or when a

hot-plug device is added to the system, or if a device that is already present in the system — but was in a

disabled or powered-down state — comes on-line.

The partial discovery process is the same as the full discovery process except that the MCTP bus owner skips the step of broadcasting a Prepare for Endpoint Discovery command in order to avoid clearing the Discovered flags of already discovered endpoints.

387 The partial discovery process may be initiated when a device that is added or enabled for MCTP sends a 388 Discovery Notify message to the MCTP bus owner. The MCTP bus owner may also elect to periodically 389 issue a broadcast Endpoint Discovery message to test for whether any undiscovered endpoints have 390 been missed. The Discovery Notify message provides the MCTP bus owner with the bus/device/function 391 or bus/function number of the MCTP PCIe endpoint. The MCTP bus owner can then send a directed 392 Endpoint Discovery message to the endpoint to confirm that the device has not been discovered. The MCTP bus owner then issues a Set Endpoint ID command to the physical address for the endpoint which 393 394 causes the endpoint to set its Discovered flag to discovered.

- 395 It is recommended that the MCTP bus owner maintains a list of the unique MCTP EIDs for the endpoints

- 396 it has discovered and reassigns the same MCTP EIDs to those endpoints if a bus/device/function or

- 397 bus/function number changes during system operation.

#### 398 Figure 3 provides an example flow of operations for partial endpoint discovery.

#### Partial PCIe MCTP Endpoint Discovery

399

400

#### Figure 3 – Flow of operations for Partial Endpoint Discovery

#### 401 **6.9.5 Endpoint re-enumeration**

If the bus implementation includes hot-plug devices, the bus owner shall perform a full or partial endpoint discovery any time the MCTP bus owner goes into a temporary state where the MCTP bus owner can miss receiving a Discovery Notify message (for example, if the bus owner device is reset or receives a firmware update). Whether a full or partial endpoint discovery is required is dependent on how much information the MCTP bus owner retains from prior enumerations.

#### DSP0238

## 407 6.10 MCTP messages timing requirements

Table 4 lists MCTP-specific timing requirements for MCTP Control messages and operation on the PCIe

VDM medium. All MCTP Control Messages over PCIe VDM shall comply to the timing specification listed

in Table 4.

411

#### Table 4 – Timing specifications for MCTP Control messages on PCIe VDM

| Timing Specification            | Symbol   | Min                              | Max                          | Description                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------|----------|----------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Endpoint ID reclaim             | TRECLAIM | _                                | 5 sec                        | Maximium interval that an endpoint is<br>allowed to be non-responsive to MCTP<br>control messages before its EID may be<br>reclaimed by the bus owner.                                                                                                                                                                                                       |

|                                 |          |                                  |                              | A bus owner shall wait at least for this interval before an EID of the non-responsive endpoint is reclaimed.                                                                                                                                                                                                                                                 |

| Number of request retries       | MN1      | 2                                | See<br>Description<br>column | Total of three tries, minimum: the<br>original try plus two retries. The<br>maximum number of retries for a given<br>request is limited by the requirment that<br>all retries shall occur within MT4, max of<br>the initial request.                                                                                                                         |

| Request-to-response time        | MT1      | _                                | 120 ms                       | This interval is measured at the<br>responder from the end of the reception<br>of an MCTP control request to the<br>beginning of the transmission of the<br>corresponding MCTP control response.<br>This requirement is tested under the<br>condition where the responder can<br>successfully transmit the response on<br>the first try.                     |

| Time-out waiting for a response | MT2      | MT1 max <sup>[1]</sup><br>+ 6 ms | MT4, min <sup>[1]</sup>      | This interval at the requester sets the<br>minimum amount of time that a<br>requester should wait before retrying a<br>MCTP control request. This interval is<br>measured at the requester from the end<br>of the successful transmission of the<br>MCTP control request to the beginning<br>of the reception of the corresponding<br>MCTP control response. |

|                                 |          |                                  |                              | NOTE: This specification does not preclude<br>an implementation from adjusting the<br>minimum time-out waiting for a response to a<br>smaller number than MT2 based on the<br>measured response times from responders.<br>The mechanism for doing so is outside the<br>scope of this specification.                                                          |

| Instance ID expiration interval | MT4      | 5 sec <sup>[2]</sup>             | 6 sec                        | Interval after which the instance ID for a given response will expire and become reusable if a response has not been received for the request. This is also the maximum time that a responder tracks an instance ID for a given request from a given requester.                                                                                              |

| Timing Specification |                                                                                                                                                                                                                                                                                                                                                                          | Symbol | Min | Max | Description |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-------------|--|

| NOTE 1:              | Unless otherwise specified, this timing applies to the mandatory and optional MCTP commands.                                                                                                                                                                                                                                                                             |        |     |     |             |  |

| NOTE 2:              | If a requester is reset, it may produce the same sequence number for a request as one that was previously issued. To guard against this, it is recommended that sequence number expiration be implemented. Any request from a given requester that is received more than MT4 seconds after a previous, matching request should be treated as a new request, not a retry. |        |     |     |             |  |

- 412 **ANNEX A**

- 413 (informative)

- 414

- 415

# Notations and conventions

# 416 **Notations**

| 417               | 417 Examples of notations used in this document are as follows: list into text needed |             |                                                                                                                                                                                                                       |  |  |  |

|-------------------|---------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 418<br>419<br>420 | •                                                                                     | 2:N         | In field descriptions, this will typically be used to represent a range of byte offsets starting from byte two and continuing to and including byte N. The lowest offset is on the left, the highest is on the right. |  |  |  |

| 421<br>422        | •                                                                                     | (6)         | Parentheses around a single number can be used in message field descriptions to indicate a byte field that may be present or absent.                                                                                  |  |  |  |

| 423<br>424        | •                                                                                     | (3:6)       | Parentheses around a field consisting of a range of bytes indicates the entire range may be present or absent. The lowest offset is on the left, the highest is on the right.                                         |  |  |  |

| 425<br>426<br>427 | •                                                                                     | <u>PCle</u> | Underlined, blue text is typically used to indicate a reference to a document or specification called out in Clause 2, "Normative References" or to items hyperlinked within the document.                            |  |  |  |

| 428               | •                                                                                     | rsvd        | Abbreviation for Reserved. Case insensitive.                                                                                                                                                                          |  |  |  |

| 429<br>430        | •                                                                                     | [4]         | Square brackets around a number are typically used to indicate a bit offset. Bit offsets are given as 0-based values (that is, the least significant bit [LSb] offset = 0).                                           |  |  |  |

| 431<br>432        | •                                                                                     | [7:5]       | A range of bit offsets. The most significant bit is on the left, the least significant bit is on the right.                                                                                                           |  |  |  |

| 433<br>434        | •                                                                                     | 1b          | The lower case " $b$ " following a number consisting of 0s and 1s is used to indicate the number is being given in binary format.                                                                                     |  |  |  |

| 435               | •                                                                                     | 0x12A       | A leading " $0x$ " is used to indicate a number given in hexadecimal format.                                                                                                                                          |  |  |  |

|                   |                                                                                       |             |                                                                                                                                                                                                                       |  |  |  |

**ANNEX B** 436 (informative) 437 438 439 440

# Change log

| Version | Date       | Description                                                                                                                                                              |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0.0   | 2009-07-28 |                                                                                                                                                                          |

| 1.0.1   | 2009-10-30 | Created erratum to clarify Length field definition of PCIe VDM header for MCTP PCIe VDM transport binding, modify introduction section, and clean up references section. |

| 1.0.2   | 2014-12-07 | Clarifications to TD bit usage. Added TLP Digest/ECRC to packet figure and to field descriptions table.                                                                  |

| 1.1.0   | 2018-10-24 | Added support for PCIe Gen 3, PCIe Gen 4, and ARI.                                                                                                                       |

|         |            | Fixed Figure 1 to cover PCIe 1.0/2.0/2.1/3.X/4.0.                                                                                                                        |

|         |            | Clarified MCTP over PCIe VDM compliant management device requirements.                                                                                                   |

|         |            | Clarified Endpoint ID reclaim definition.                                                                                                                                |

|         |            | Clarified MCTP bus owner requirements in the specification.<br>Eliminated PCIe bus owner term and replaced it with PCIe root<br>complex where applicable.                |

| 1.2.0   | 2021-03-02 | Added support for PCIe Gen 5.X, CXL 1.X, and CXL 2.X.                                                                                                                    |

441